همکاری IBM و سامسونگ در طراحی تراشه با پروسه VTFET – عمر باتری اسمارتفونها به یک هفته میرسد؟

نمایش خبر

| تاریخ : 1400/9/29 نویسنده: مسعود بهرامی شرق | ||

| برچسبها : | آی بی ام IBM ، باتری Battery ، سامسونگ Samsung | |

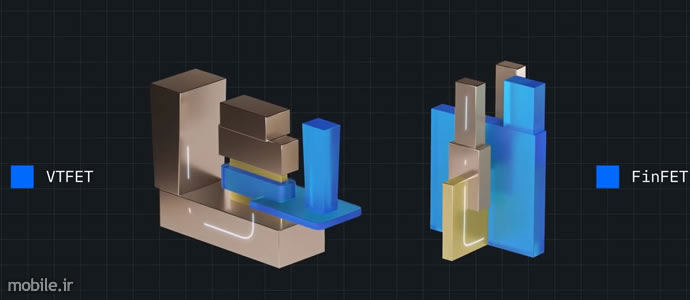

اکثر چیپستهای مدرن امروزی (از جمله اسنپدراگون موجود در گوشیهای اندرویدی یا A15 بایونیک در آیفونهای جدید) بر مبنای پروسه FinFET توسعه یافتهاند. توضیح کامل سازوکار این پروسه خارج از بحث این مطلب است، اما به زبان ساده، در پروسه FinFET ترانزیستورهای موجود در تراشه با چیدمان افقی روی یک صفحه تخت در کنار هم قرار گرفتهاند و جریان الکتریکی نیز طبیعتا به شکل عرضی و پهلو-به-پهلو بین ترانزیستورها حرکت میکند.

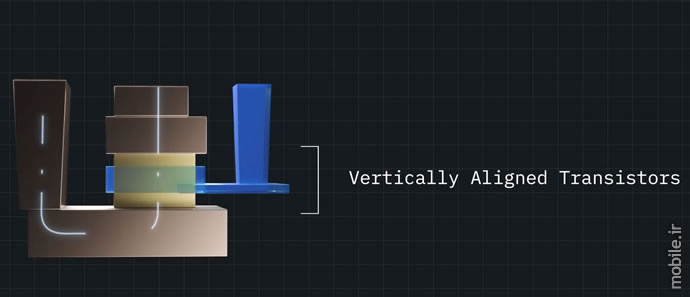

چنانچه بخواهیم از یک سو به تعداد ترانزیستورها افزوده و از سوی دیگر فضای فیزیکی تراشه را زیادتر نکنیم، تنها راه (به جز کوچکتر کردن ترانزیستورها) آن است که یک ردیف بالاتر رفته و ترانزیستورها را به شکل عمودی روی هم بچینیم. این چیدمان عمودی – که شاهکلید طراحی جدید IBM و سامسونگ است – طراحی VTFET نامیده میشود. VTFET کوتاهشده Vertical Transport Field Effect Transistors بوده و میتوانیم آن را «ترانزیستورهای انتقال اثر میدان عمودی» معنا کنیم. IBM و سامسونگ با چیدن ترانزیستورها روی هم، میتوانند برخی محدودیتهای طراحی FinFET را دور زده و طول گیت (gate length) ترانزیستور را بهینه کنند.

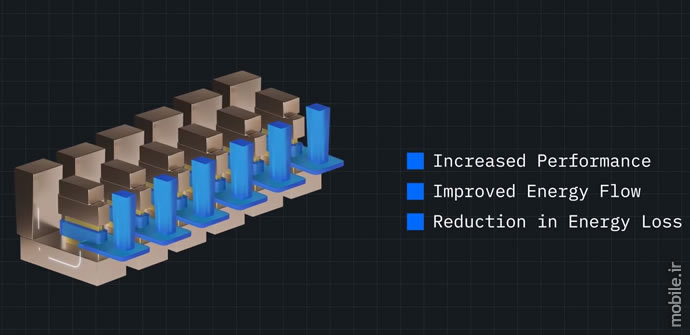

از طراحی جدید VTFET میتوان به دو شیوه متفاوت بهره گرفت؛ رویکرد اول آنکه هدف نهایی این طراحی را صرفهجویی در مصرف قرار دهیم. به گفته IBM، در این پروسه جدید، با افزایش نقاط تماس ترانزیستورها، عبور جریان بیشتر شده و انرژی کمتری هدر میرود. به این ترتیب، طبق ادعای IBM میتوان عمر باتری را تا 85 درصد افزایش داد و مشکل شارژ کردنهای متوالی باتری اسمارتفونها را حل کرد. البته، با اتخاذ این رویکرد تغییر چندانی در قدرت تراشه اتفاق نمیافتد و عملکرد آنها تقریبا همپای تراشههای مدرن با معماری ARM خواهد بود (مثل همان چیپستهای اسنپدراگون و بایونیک).

رویکرد دوم آن است که به جای مصرف انرژی، قدرت چیپست را هدف قرار دهیم. به این ترتیب، میتوان عملکرد تراشههای ساخته شده با پروسه VTFET را تا 100 درصد نسبت به همتایان FinFET افزایش داد. این امر نیز اتفاق بزرگی در صنعت نیمهرسانا خواهد بود، اما باید به این نکته توجه داشته باشیم که در این رویکرد، میزان مصرف انرژی تغییری نکرده و در حد همان تراشههای امروزی باقی میماند.

در حال حاضر، تمام موارد ذکر شده بر پایه پیشنمونههای آزمایشی گزارش شده، اما متخصصان IBM بر این باورند که این طراحی جدید پتانسیل آن را دارد که در مقیاسی فراتر از نانوشیت (صفحه نانو) به تولید برسد. این بدان معناست که گذار از مرحله پیشنمونه ساده تا تولید انبوه تراشه بر مبنای VTFET، چندان هم دشوار نخواهد بود.

کاربردهای بالقوه طراحی جدید VTFET فراوان است. صرفهجویی در مصرف و افزایش عملکرد – که به آن اشاره شد – خواسته تمام سازندگان دیوایسهای الکترونیک است. طبق ادعای IBM، عمر باتری در اسمارتفونهای مجهز به این نوع تراشه، میتواند به یک هفته کامل برسد! با توجه به هیاهوی فراوان در حوزه بلاکچین، یکی دیگر از کاربردهای مهم پروسه VTFET کاهش مصرف دستگاههای استخراج ارز دیجیتال است.

عرصه دیگری که به شکل قابلتوجهی از مزایای پروسه VTFET بهرهمند خواهد شد، اینترنت اشیا (IoT) است. به لطف این پروسه جدید، میتوان دیوایسهای کوچکتر با مصرف کمتری را در حوزه IoT متصور شد. همچنین میتوان دامنه استفاده از این دیوایسها را به محیطهای مختلفی گسترش داد از جمله در شناورهای اقیانوسی، اتومبیلهای خودران و فضاپیماها.

نکته جالب دیگر در رابطه با طراحی جدید VTFET، تأیید قانون مور و رسمیتبخشی مجدد به این قانون است. طبق این قانون – که در سال 1965 توسط گوردون مور تدوین شد – تعداد ترانزیستورهای موجود در چیپها هر دو سال یک بار، دو برابر میشود. با توجه به افزایش ترانزیستورها و فضای محدود تراشهها، برخی کارشناسان به این نتیجه رسیدند که قانون مور دیگر در دنیای نیمهرساناها صدق نکرده و حتی برخی با ارائه «قانون کومی»، پیشنهاد کردند که این قانون جدید جایگزین قانون مور شود. اما با طراحی VTFET و چیدمان عمودی ترانزیستورها روی هم، مشکل کمبود فضا حل شده و بار دیگر میتوان به قانون مور اعتبار بخشید.

طراحی جدید VTFET تلاش دیگری از سوی IBM برای کاهش رد پای ترانزیستور در تراشهها به شمار میرود. بد نیست بدانید، در ماه می، IBM از تکنولوژی معماری 2 نانومتری خود رونمایی کرد. با استفاده از این پروسه میتوان تا 50 میلیارد ترانزیستور را روی تراشهای به اندازه ناخن انگشت جا داد.

در پایان لازم به ذکر است، پروسه VTFET شباهت فراوانی به ماژولهای حافظه V-NAND دارند که در آنها سلولهای حافظه روی هم سوار میشوند. همچنین، چیدمان عمودی در عرصه نیمهرساناها، چندیست که به یک گرایش تبدیل شده و به عنوان مثال، نقشه راه آینده اینتل نیز به این سمت تمایل دارد. البته نخستین کار اینتل در این حیطه، روی چیدمان عمودی اجزای تراشه تمرکز داشت نه ترانزیستورها. گفتنیست، اینتل هم برای جایگزین کردن پروسه FinFET برنامههایی دارد، از جمله پروسه RibbonFET که در تابستان از آن رونمایی کرد. از قرار معلوم، محصولات نیمهرسانای اینتل با نام نسل 20A – که قرار است در سال 2024 به تولید برسند – از این تکنولوژی استفاده خواهند کرد.

-

آشنایی با Infinix Note 50s 5G - میانرده معطر Infinix با Dimensity 7300 و نمایشگر خمیده +FHD

آشنایی با Infinix Note 50s 5G - میانرده معطر Infinix با Dimensity 7300 و نمایشگر خمیده +FHD

-

شیائومی Poco X7 Pro در نگاه رسانهها – نقاط ضعف و قوت از دید حرفهایها

شیائومی Poco X7 Pro در نگاه رسانهها – نقاط ضعف و قوت از دید حرفهایها

-

معرفی سامسونگ Galaxy M56 با ضخامت کمتر، پشت و روی شیشهای و عقبگرد در پردازنده و اسپیکر

معرفی سامسونگ Galaxy M56 با ضخامت کمتر، پشت و روی شیشهای و عقبگرد در پردازنده و اسپیکر

-

معرفی Moto Pad 60 Pro – تبلت جدید موتورولا با Dimensity 8300 و قلم استایلوس

معرفی Moto Pad 60 Pro – تبلت جدید موتورولا با Dimensity 8300 و قلم استایلوس

-

بازگشت Acer به دنیای اسمارتفون با معرفی Super ZX Pro و Super ZX

بازگشت Acer به دنیای اسمارتفون با معرفی Super ZX Pro و Super ZX

-

معرفی nubia RedMagic 10 Air گوشی مخصوص بازی نوبیا با باتری 6,000mAh و ضخامت 7.85 میلیمتری

معرفی nubia RedMagic 10 Air گوشی مخصوص بازی نوبیا با باتری 6,000mAh و ضخامت 7.85 میلیمتری

-

معرفی Honor Power میانرده آنر با Snapdragon 7 Gen 3 و باتری رکوردشکن 8,000 میلی آمپر ساعتی!

معرفی Honor Power میانرده آنر با Snapdragon 7 Gen 3 و باتری رکوردشکن 8,000 میلی آمپر ساعتی!