TSMC، نخستین طراح چیپست با فناوری 5 نانومتری

نمایش خبر

| تاریخ : 1398/1/22 نویسنده: مسعود بهرامی شرق | ||

| برچسبها : | پردازنده Processor ، تی اس ام سی TSMC | |

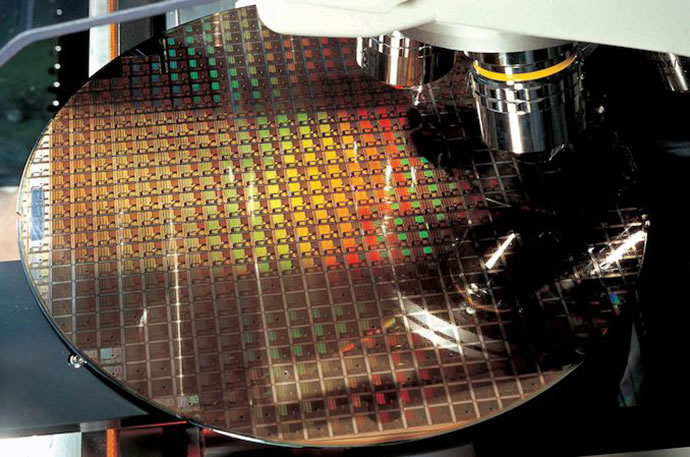

واحد خبر mobile.ir : کمپانی تایوانی TSMC در روز چهارشنبه 3 آوریل 2019 (14 فروردین 1398)، اعلام کرد که زیرساخت مورد نیاز برای طراحی چیپست با تکنولوژی 5 نانومتری (N5) در پلتفرم اختصاصی OIP (پلتفرم نوآوری باز) به طور کامل آماده شده است. به گفته TSMC، این زیرساخت، امکان تولید چیپستهای 5 نانومتری برای نسل آینده دیوایسهای موبایل و سایر کاربریهایی که به توان پردازشی بالا نیازمند است را فراهم نموده و صنعت را برای پذیرش هرچه بیشتر 5G و هوش مصنوعی آماده میکند. مهمترین فروشندگان محصولات مبتنی بر مالکیت معنوی (IP) و "اتوماسیون طراحی الکترونیک" (EDA)، نیز در توسعه و ارزیابی این زیرساخت با TSMC همکاری داشتهاند.

پروسه 5 نانومتری TSMC چندیست که در تولید ریسکپذیرانه چیپست به کار گرفته شده و سطح جدیدی از عملکرد و بهینهسازی انرژی را در اختیار طراحان IC قرار میدهد. طبق ادعای شرکت سازنده، چیپستهای ساخته شده TSMC با پروسه 5 نانومتری (و بر مبنای معماری هسته ARM Cortex-A72) از لحاظ تراکم منطق 1.8 برابر و از نظر سرعت 15 درصد سریعتر از تراشههایی هستند که در همان معماری با پروسه 7 نانومتری ساخته شده باشند.

پروسه 5 نانومتری TSMC، دومین نسل از تکنولوژی تولید این کمپانی است که همزمان از دو لیتوگرافی DUV (ماوراء بنفش عمیق) و EUV (ماوراءبنفش شدید) استفاده میکند. در پروسه N5، میتوان برای ارتقای تراکم، لیتوگرافی EUV را تا 14 لایه استفاده کرد (مقایسه کنید با پروسه N7+ که لیتوگرافی EUV نهایتا تا 4 لایه استفاده میشد).

توسعه فناوری N5 چندی پیش توسط TSMC به پایان رسید و نخستین مشتریهای این کمپانی، با دسترسی به ابزارهای پیش تولید، از مدتی قبل تولید ریسکپذیرانه چیپست را با استفاده از N5 آغاز کردهاند. زیرساخت جامع طراحی 5 نانومتریِ TSMC شامل "راهنمای ضابطه طراحی" (DRM) 5 نانومتری، "کیتهای طراحی پروسه" (PDKs) و مدل SPICE (برنامه شبیهسازی با تأکید بر IC) بوده و از طیف کاملی از ابزارهای تصدیقشده EDA نیز پشتیبانی میکند. مشتریان به پشتوانه منابع پلتفرم اختصاصی OIP – که TSMC آن را بزرگترین اکوسیستم طراحی در صنعت میداند – طراحیهای گستردهای را آغاز کرده و راه را برای مرحله tape-out، فعالیتهای آزمایشی و نمونهگیری هموار کردهاند.

به گفته کلیف هو (Cliff Hou)، معاون تحقیق و توسعه TSMC، تکنولوژی 5 نانومتری TSMC پیشرفتهترین پروسه منطقی مورد نیاز برای هوش مصنوعی و 5G را ارائه میکند. تکنولوژی 5 نانومتری به همکاری عمیقتری در زمینه طراحی و بهینهسازی نیاز دارد. از این رو ما به همکاری خود با شرکا ادامه میدهیم تا بلوکهای IP اعتباریافته سیلیکونی و ابزارهای EDA را برای استفاده مشتریان آماده کنیم.

علاوه بر ابزارهای TSMC، توسعهدهندگان چیپست میتوانند مجموعه کاملی از ابزارهای EDA را از کمپانیهایی مثل ANSYS ،Cadence ،Mentor Graphics و Synopsys نیز تهیه کنند. به گفته TSMC، برنامههای EDA که توسط شرکتهای مذکور ارائه میشوند هم کاملا از N5 DRM پشتیبانی کرده و لذا از بابت دقت، قابلیت روت شدن برای بهینهسازی انرژی و دیگر جنبههای این تکنولوژی، نگرانی خاصی وجود نخواهد داشت. بدیهیست که تمام ابزارها از سوی پیمانکارِ نیمهرساناها، تأیید شدهاند.

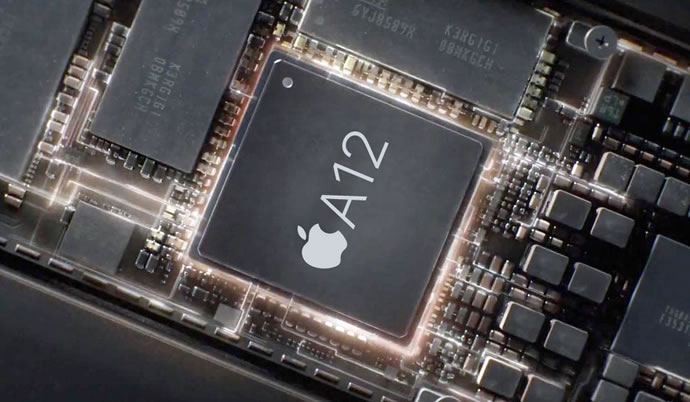

احتمالا میدانید که کمپانی تایوانی TSMC از سال 2016، تنها تأمینکننده چیپستهای سری A برای شرکت اپل بوده است. به گفته برخی منابع نزدیک به اپل، تمام سفارشهای این شرکت آمریکایی برای تولید تراشههای A11 Bionic ،A10 Fusion و A12 Bionic به TSMC داده شده است. از همین رو، انتظار میرود TSMC تنها تأمینکننده نسل بعدی تراشههای سری A باشد.

گفته میشود آیفونهای امسال به چیپستهای A13 (با لیتوگرافی 7nm+) مجهز میشوند. با توجه به خبر جدید TSMC، میتوان امیدوار بود که در آیفونهای بعدی شاهد تراشههای 5 نانومتری از سری A باشیم که به احتمال زیاد در آیفونهای سال 2020 به کار خواهند رفت.

البته دیوایسهای اندرویدی نیز از این تکنولوژی بینصیب نخواهند ماند. کمپانی کوالکام تلاش کرده تا نه تنها از لحاظ عملکرد، بلکه در پروسههای تولید (که روز به روز کوچکتر میشوند) نیز فاصله بین پروسسورهای پرچمدار اسنپدراگون و تراشههای سری A را کمتر نماید. با این اوصاف، ممکن است کمی بعد از عرضه تراشه A13، کوالکام از تراشههای 5 نانومتری اسنپدراگون رونمایی کند.

در پایان لازم به ذکر است که TSMC و شرکایش موفق به توسعه معماری جامعی از مالکیت معنوی برای تکنولوژی N5 شدهاند که در حال حاضر عمدتا روی HPC (پردازش با عملکرد بالا) و چیپستهای موبایل متمرکز است. Foundation IP یا بنیاد مالکیت معنوی TSMC، مجموعههای با چگالی و عملکرد بالایی از کتابخانههای سلولی استاندارد و کامپایلرهای حافظه را شامل میشود. در این میان، شرکای TSMC انواع مختلفی از هستههای IP را برای چیپستهای N5 ارائه میکنند که از آن جمله میتوان به DDR ،LPDDR ،MIPI ،PCIe و USB PHYs اشاره کرد.

-

معرفی میانردههای +vivo Y300 Pro با باتری 7,300mAh و Y300t با باتری 6,500mAh

معرفی میانردههای +vivo Y300 Pro با باتری 7,300mAh و Y300t با باتری 6,500mAh

-

معرفی Redmi 13X ارزانقیمت شیائومی با صفحهنمایش 90 هرتزی، دوربین 108MP و پردازنده Helio G91

معرفی Redmi 13X ارزانقیمت شیائومی با صفحهنمایش 90 هرتزی، دوربین 108MP و پردازنده Helio G91

-

معرفی Realme 14 5G با Snapdragon 6 Gen 4، بدنه IP69 و باتری 6,000mAh

معرفی Realme 14 5G با Snapdragon 6 Gen 4، بدنه IP69 و باتری 6,000mAh

-

معرفی پایینرده ارزانقیمت vivo Y39 5G با پردازنده 4 نانومتری و باتری 6,500mAh

معرفی پایینرده ارزانقیمت vivo Y39 5G با پردازنده 4 نانومتری و باتری 6,500mAh

-

معرفی Poco F7 Ultra اولین اولترای پوکو با Snapdragon 8 Elite، اثر انگشت اولتراسونیک و دوربین پریسکوپی

معرفی Poco F7 Ultra اولین اولترای پوکو با Snapdragon 8 Elite، اثر انگشت اولتراسونیک و دوربین پریسکوپی

-

معرفی Poco F7 Pro با Snapdragon 8 Gen 3، فریم آلومینیومی، استاندارد IP68 و باتری 6,000mAh

معرفی Poco F7 Pro با Snapdragon 8 Gen 3، فریم آلومینیومی، استاندارد IP68 و باتری 6,000mAh

-

سامسونگ Galaxy A56 در نگاه رسانهها – نقاط ضعف و قوت از دید حرفهایها

سامسونگ Galaxy A56 در نگاه رسانهها – نقاط ضعف و قوت از دید حرفهایها